News and updates

April 10th, 2024: OpenASIP enables R-Blocks, a compiler-programmable CGRA

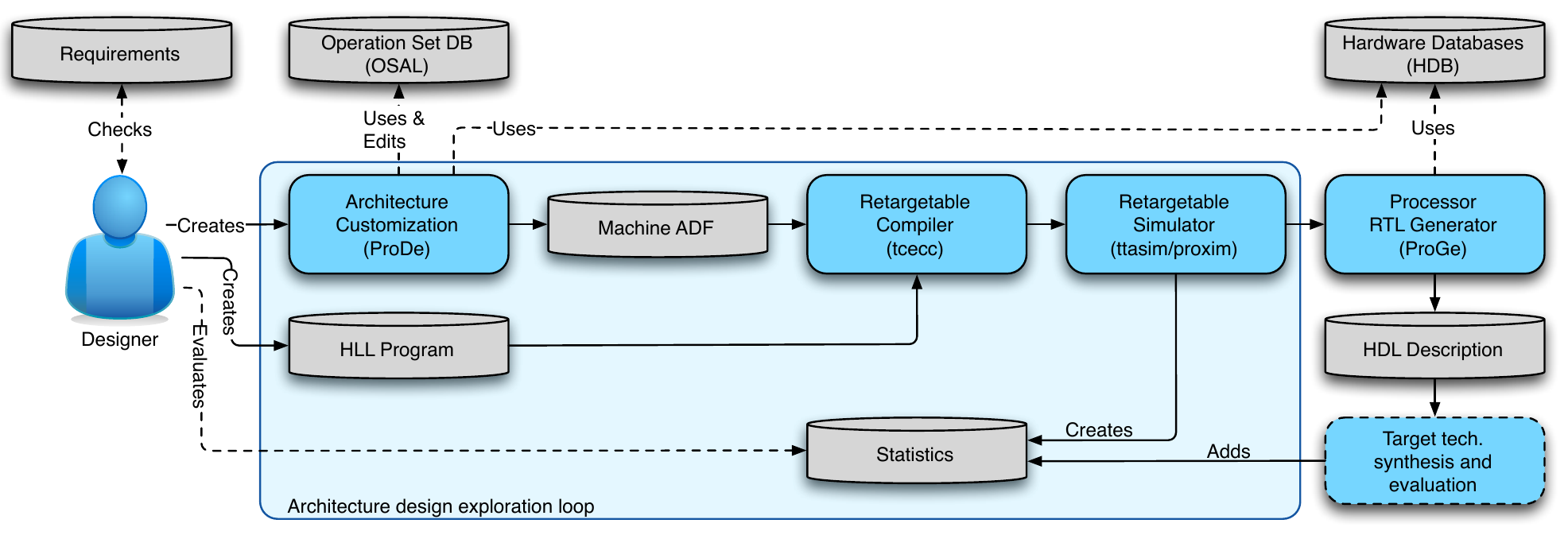

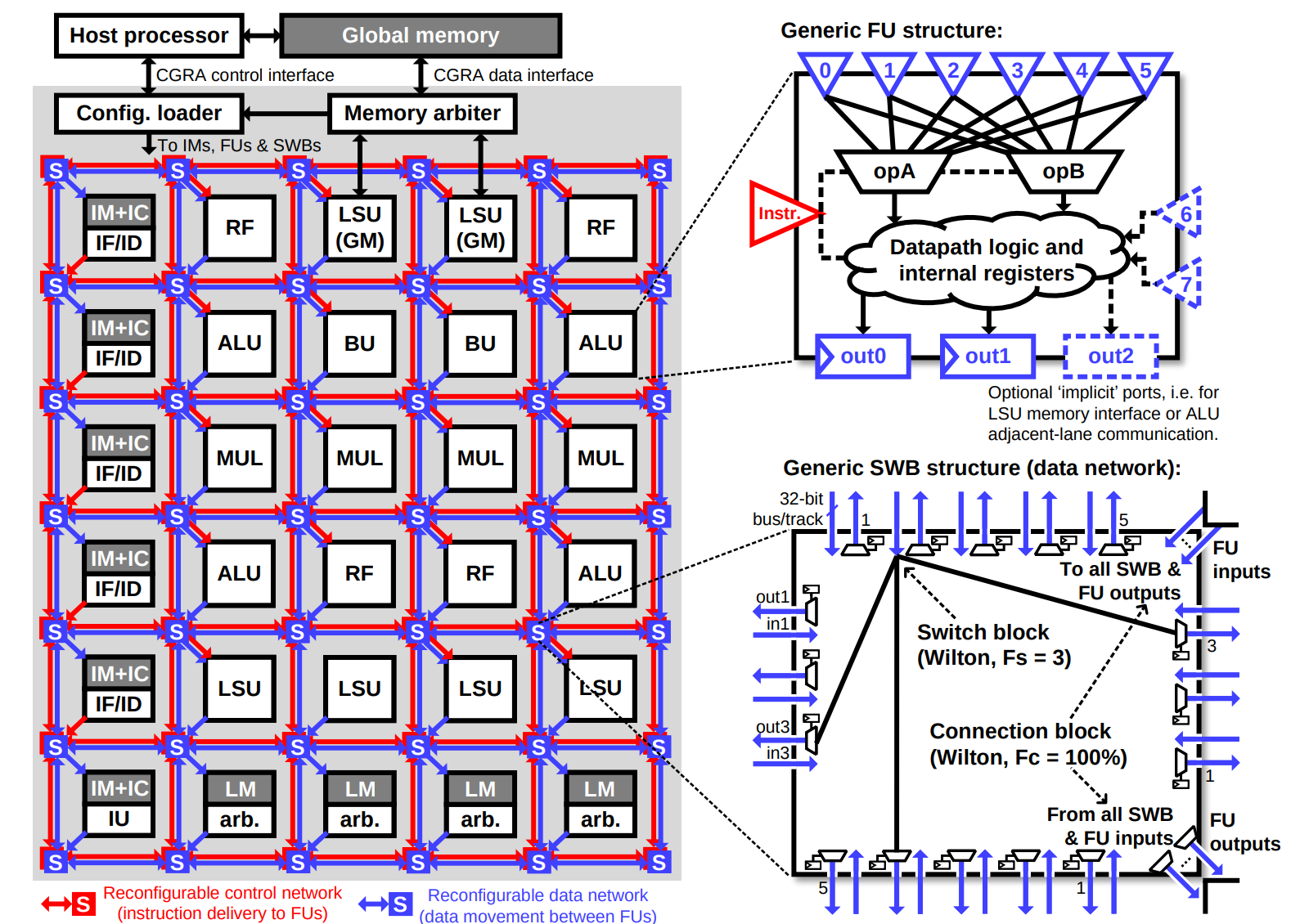

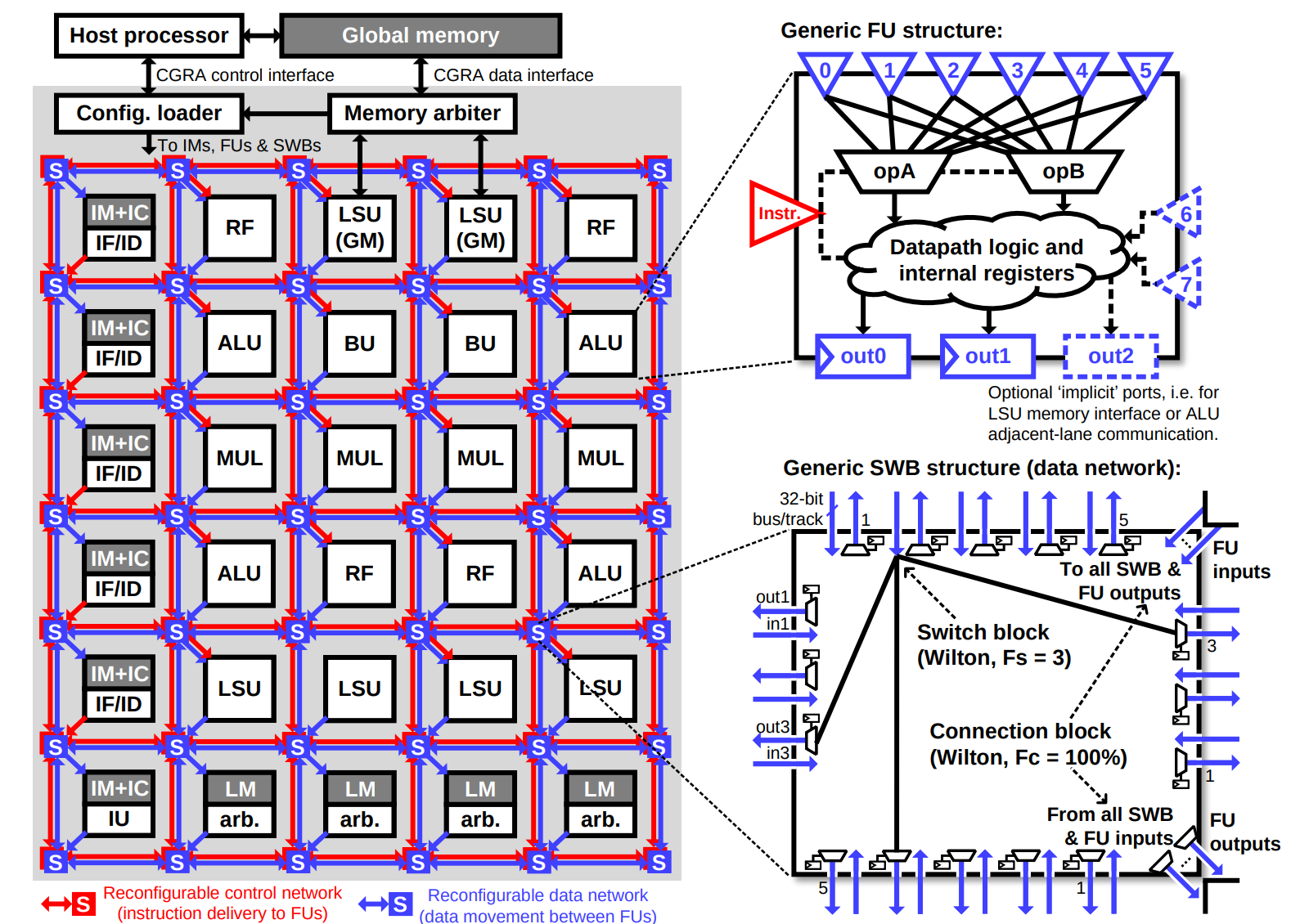

As a result of collaboration between Eindhoven University of Technology, Netherlands and Tampere University, Finland, the work on R-Blocks, an ultra low power coarse-grained reconfigurable array CGRA was published in ACM Transactions on Reconfigurable Technology and Systems (TRETS). CGRAs have been proposed as a flexible yet energy-efficient platform. Thanks to OpenASIP's flexible architecture description template and retargetable compiler, R-Blocks is the first compiler-programmable CGRA. Read the publication here.

February 16th, 2024: OpenASIP-based RISC-V function unit generation from Gebze Technical University

In a recent work Yanık et al. used OpenASIP toolset as a basis for rapidly extending the instruction set of RISC-V cores. They use Vitis HLS tool to generate custom function units (FU) directly from C program descriptions. What a great idea! The user needs to only give the description of the custom operation in C and the tools generate a full function unit out of it. After that, their scripts integrate the function unit into a RISC-V ASIP using OpenASIP. It’s great to see how our easy-to-use custom FU integration enables people to create experiments like this.

Their paper DELTA-V: An Open-Source High-Level Synthesis Driven ASIP Design Automation Tool for RISC-V Microprocessors was published in 2023 14th International Conference on Electrical and Electronics Engineering (ELECO). The paper is available here and the source code here.

A new version of OpenASIP released! See the

change summary

for more details. Install instructions can be found in the README.

December 11th, 2023: OpenASIP-designed audio coprocessor

from University of Turin

Interesting audio processor case study designed with OpenaASIP was

published by University of Turin researchers who received good

results even while using a fully connected interconnection matrix:

The power consumption of the developed TTA architecture was found

to be significantly lower compared to traditional software-based

approaches, with a total estimated power of approximately 350 mW.

Details can be found in the

publication

and the

master's thesis.

The first OpenASIP version with preliminary RISC-V customization support is now out!

July 23rd, 2018: A tutorial slide deck with clickable videos uploaded

The slide set (39M)

contains clickable videos and goes through most of the tool set. It was first presented

in OpenSuco 3 workshop organized within the ISC High Performance 2018 conference (June 28th in Frankfurt, Germany).

A demonstration featuring a neural network coprocessor designed with OpenASIP

was shown at CIVIT.